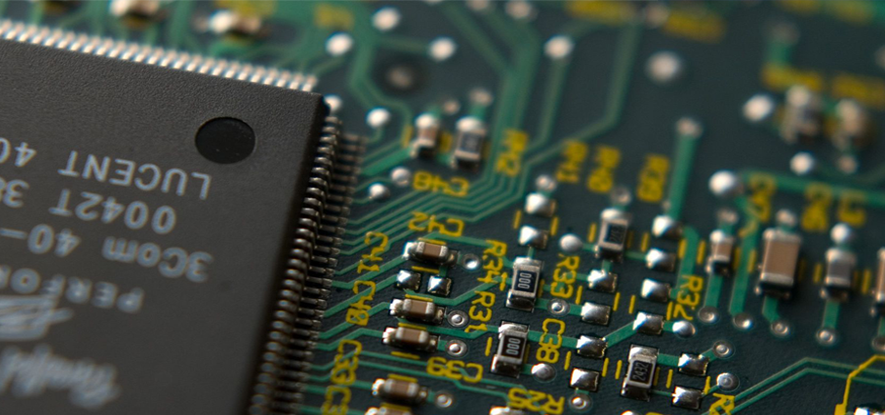

we can take any specification or an existing design and execute the complete RTL Design, Integration, Verification, STA-Synthesis, Physical design and DFT and tapeout a design.

To achieve this capability Agasthya Space has its own flows and processes, Project Management team, an expert senior core team, one of the best engineering teams and experience in taping out multiple designs.

Design

We understand the relationship between specification and implementation, and know how to partition designs and make trade-offs necessary for performance, power and area. Our team of engineers are fully capable of taking responsibility of RTL development for IP/ASIC/SOC/FPGA using Verilog, VHDL and System Verilog. With our extensive domain knowledge in developing IP/ASIC/SOC/FPGA on latest interface protocols e.g. Ethernet, SAS, FC, PCIe, USB, SATA, MIPI, DDR, AMBA etc. we can help integrate IP into larger subsystem or complete SOC with other blocks including processors.

Digital Design Expertise

|

• SOC Design

• Micro Architecture

• RTL Coding

|

• Linting & CDC

• IP & SOC Integration

• Synthesis

|

• Timing

• Performance

• Low Power

|

Physical design

Our proven physical design flow, methodologies and rich experience enable us to deliver physical design implementation with superior performance. We have dedicated experts for each design stage, methodology & tools and have undertaken projects across Networking, Mass Storage and Mobile for Area, Power & Time optimization. Interface expertise includes MIPI, DDR, PCIe, SATA, USB, AMBA etc.

Physical Design Expertise

|

• Top and block level physical implementation

• Analog block integration

• Low Power Methodology

• Floor planning & Partitioning

• Clock tree Synthesis

• Place/Route

• Scan Recording

|

• Timing Closure

• Signal Integrity Analysis

• Power/EM/IR/Noise

• DFT, BIST, SCAN & ATPG

• Physical Verification

• Custom Layout

|

Verification

Our team has extensive experience in taking up full responsibility or being part of larger customer team, delivering module to full-chip verification for complex chips. We have worked with simple verification environment created using simple Verilog or VHDL to full coverage driven random environment in System Verilog using UVM. Our team has developed reusable Verification components from scratch as well as used industry standard Agasthya as part of environment to reduce time and improve quality of verification. We have verified multiple chips, pre and post silicon, to ensure highest quality working chips.

Digital Verification Expertise

|

• Strategic Planning

• Functional Planning

• Constrained random

• Coverage driven

|

• Assertion based

• Timing driven

• Performance driven

• Power driven

|

• Formal

• Gate level

• Post silicon

|

Dft

Our mission is to provide proven DFT services using an industry standard Design-for-Test tool set and to ensure an optimized design as per customer requirements Our DFT service engage customers worldwide and provide wide range of consulting options to suit customer budget and schedule. Our DFT services can dramatically impact production test times and costs.

Our DFT Services help customer address the growing challenges faced when moving to smaller process nodes and more complex, low-power, mixed-signal systems-on-chip (SoCs). Using PerfectVIP broad span of industry leading technologies, our DFT consultants have a track record of success. Our team will help you step through the entire process and find ways to increase yields while decreasing delays.

From design to installation, our engineers work closely with customers to provide test engineering solutions. We evaluate product test flow and cycle time optimization to maintain test efficiency.

We provide the following services related to DFT:

|

|

Scan

• Scan stitching

• Scan compression

• Scan design architecture

• ATPG and Simulations

|

|

JTAG & Boundary Scan

• DFT Tools

• Simulation Tools

Memory BIST

• Memory Fault models and BIST architecture

|

Analog and Mixed signal

Agasthya has team of analog designers that utilizes the latest designing techniques and design tools to face the analog and mixed signal challenges. The mixed signal team has the expertise to develop or migrate mixed signal designs ranging from high speed SERDES to standard cell libraries, memories and power circuits efficiently. The etam has domain expertise to handle the complex and challenging analog circuit requirements including to build mixed signal verification environments for sophisticated mixed signal ICs.

Services Offered:

• Customization to other Foundries/ nodes and emerging standards

• Porting to other Foundries

o Customization to other Foundries/ nodes and emerging standards

o Porting to other Foundries

• Analog Macro Specifications

• Design

o High-speed IO design

o Seredes

o IO libraries

o Power management units

o Low power custom circuit design

o PLL

o PHY

o DACs and ADCs

o IP conversion: new process nodes & technologies

o Switching and linear regulators

o Op-amps

• Custom Layout

o We have layout experience on analog circuits including various types of ICs.

• AMS Verification and Modeling including modeling process, voltage and temperature effects & variety of noise sources

• Verification & Characterization

o Agasthya has a team of AMS design and verification experts who can build state of the art mixed signal verification environments for mixed signal ICs. Our team has built complex verification environments from scratch, written self-checking assertion checks and developed randomize & custom test cases.

• Integration with Digital Logic